PARTS

Parallel Architectures for Real-Time Systems

is a research center active in the domains of real-time and embedded systems.

Created in 2006, it is a transdisciplinary research unit of the Sciences Faculty and the Polytechnic School at the ULB.

Adopted approach is based on the extension of the well known co-design paradigm: to the concept of simultaneous SOFTWARE/HARDWARE design, we append the aspects of TECHNOLOGY used for integrated circuit manufacturing.

By exploiting THEORY/SOFTWARE/HARDWARE/TECHNOLOGY quadruplet, the goal is to holistically design predictable, optimized and efficient parallel real-time systems.

PARTS is built on the willingness to join fundamental and applied R&D and move the codesign approach to the next level by combining:

In Real-Time Systems, correctness depends on the results of computations but also on the time at which they are produced. A Real-Time System is required to complete its work and deliver its services on a timely basis. In other words, Real-Time Systems have stringent timing requirements that they must meet.

Examples of Real-Time Systems include digital control, traffic, command and control, signal processing, flight control systems and telecommunication systems.

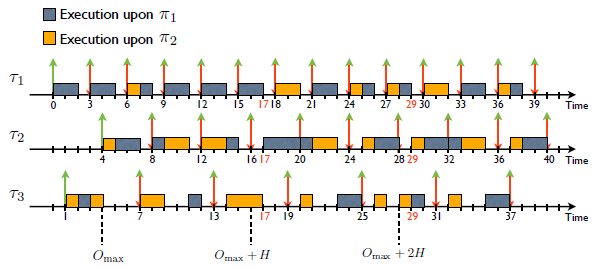

Real-time scheduling theory concerns task models, scheduling algorithms, platform models and schedulability analysis.

With Real-time Operating Systems design we are capable to validate in real cases the algorithms and designs proposed by the Real-time Theory, by integrating them into a flexible OS on a real platform.

These algorithms perform smart task handling and are able to take into account multiple constraints simultaneously. Typically, these algorithms manipulate: execution time, power dissipation, thermal aspects, etc. Since we are targeting fully integrated systems, application mapping, off-line/on-line resource optimization are also taken into account.

HARDWARE part consist in the design and implementation of Multi-Processor Systems-on-Chip (MPSoC). The MPSoC uses multiple CPUs along with other hardware subsystems to implement a system. These systems are widely used in networking, communications, signal processing, and multimedia among other applications.

The MPSoC platforms use existing building blocks for processing elements and memory. For systems with higher degree of parallelism, the communication is covered by Network-on-Chip (NoC). However, in order to enhance the performance of the system as a whole, and the Operating System in particular, i.e. scheduler, dedicated hardware services are developed and integrated into existing components on both computational and communicational (NoC) components. The requirements for these services are typically set during task scheduler design time.

Yesterday we co-designed software-hardware. Today we need to co-design software-hardware and the technology used for the integrated circuit manufacturing. Both sides, design and technology, are confronted with the need to understand the other in order to overcome new scaling induced issues.

Emerging technologies for advanced integrated circuit manufacturing and packaging, such as 3D-Stacked Integrated Circuits, are offering enormous potential for design of complex, highly optimized, and heterogeneous systems (memory-on-logic, logic-on-logic etc.). The design of the specific operating systems schedulers and the MPSoC platforms take into account the potential advantages of such technologies for even more optimized real-time systems (for example by combining high-performance/high-power with low-performance/low-power integrated circuits dies in the same package).