Ordonnancement efficace de systèmes embarqués temps réel strict sur plates-formes hétérogènes

by Xavier Poczekajlo

From Fri 30 Oct 2020 16:00 to Fri 30 Oct 2020 18:00

Défense publique

Bonjour à tous,

J'ai le plaisir de vous inviter à la soutenance publique de ma thèse de doctorat.

Le titre de ma thèse est le suivant: “Ordonnancement efficace de systèmes embarqués temps réel strict sur plates-formes hétérogènes”.

La thèse a été supervisée par le Professeur Joël Goossens.

La défense aura lieu vendredi 30 octobre à 16h00.

Du fait de la crise sanitaire, la défense se déroulera en ligne à cette adresse : réunion-teams

Bien à vous,

Xavier Poczekajlo

Informations pratiques

le 30 octobre 2020.

de 16h à 18h.

- 9:30am — Welcome

10am — Keynote Talk Prof. Luis Almeida (University of Porto, Portugal)

Flexible Time-Triggered Switched Ethernet: Towards Flexible/Open Cyber-Physical Systems

The Flexible Time-Triggered Switched Ethernet (FTT-SE) protocol was proposed in 2006 as a realization of the FTT paradigm specifically adapted to switched Ethernet. This paradigm is a framework to develop distributed real-time systems that are reconfigurable and adaptive. It has been successfully used for dynamic Quality-of-Service (QoS) management in control applications and video transmission, and for dynamic reconfiguration of real-time systems that are either open or include subsystems that operate occasionally. It is particularly suited to support dynamic and adaptive resource reservation in network resources through virtual channels.

In the realm of real-time Ethernet protocols, FTT-SE flexibility features with real-time guarantees are unique, possibly comparable to much more costly solutions, only, such as layer 3 or 2.5 carrier grade switches with RSVP-TE or MPLS, AVBridges or Software-Defined Networks (SDNs).

In this talk we highlight recent FTT developments in the context of switched Ethernet technology. We start with FTT-SE protocol basics and then discuss how to improve performance and robustness with the HaRTES switch that is an FTT-enabled Ethernet switch, as well as scalability and dependability of FTT-SE/HaRTES systems. We end with several use cases that show the features of these systems.

Bio

Luis Almeida is currently an associate professor at the Electrical and Computer Engineering Department of the University of Porto and a member of the Institute of Telecommunications in Porto where he coordinates the Distributed and Real-Time Embedded Systems Lab. He is also a member of the IEEE Computer Society, IFIP Tecnical Committee on Embedded Systems, EMSIG EDAA Special Interest Group on Embedded Systems Design (vice-chair), RoboCup Federation (trustee) and the Portuguese RoboCup National Committee (vice-president).

His current interests are real-time communication protocols for Cyber-Physical Systems with an emphasis on mechanisms to support predictable operational flexibility as needed for dynamic QoS management, graceful degradation and open distributed real-time systems in general. He co-authored over 250 refereed publications, 4 patents and 10 book chapters. He regularly participates in the organization and program committees of scientific events in the Real-Time Systems, Industrial Systems and Robotics communities, including RTSS, ECRTS, DATE, SIES, WFCS, ETFA and RoboCup.

11:15am — Coffee break

- 11:30 — “Why and how to map real-time core-to-I/O flows over a Tilera-like Network on Chip?”, Laure Abdallah, Mathieu Jan, Jérôme Ermont & Christian Fraboul

- 12:00pm Lunch

- 1:00pm — “Bringing Dynamicity to Real-Time Systems Through the Use of Dynamic Mesh Networking”, Florian Greff, Ye-Qiong Song, Laurent Ciarletta & Arnaud Samama

- 1:30pm — “Buffer Dimensioning based on FA Approach in the AFDX Context”, Nassima Benammar, Henri Bauer, Frédéric Ridouard & Pascal Richard

- 2pm — “Reliability of CAN-Based Distributed Real-Time Systems”, Arpan Gujarapi & Björn B. Brandenburg

- 2:30pm — Coffee break

We move to room “Forum F.”

- 3:00pm — “FTT-OpenFlow, on the way towards real-time SDN”, Cédric Ternon, Jean-Michel Dricot & Joël Goossens

- 3:30pm — “Extended Recursive Analysis for Tilera and KalRay-like NoC Architectures”, Hamdi Ayed, Jérôme Ermont, Jean-luc Scharbarg & Christian Fraboul

- 4:00pm Closing remarks

- Joël Goossens (ULB, Brussels, Belgium)

- Pierre Manneback (UMons, Mons, Belgium)

- Jean-Michel Dricot (ULB, Brussels, Belgium)

- 9:30am — Welcome

10am — Keynote Talk

“Real-Time Scheduling on Heterogeneous Multiprocessors”

By Dr. Gurulingesh Raravi (University of Porto, Portugal)

Abstract

Heterogeneous processing platforms are spreading at an unprecedented rate in embedded systems thanks to the availability of multicore processors. These platforms span diverse areas of our life right from smart phones to health-care to autonomous vehicles. They have emerged as today's computational workhorse for both desktop and embedded systems; just like the single-core processor was in the past. Every major semiconductor company is offering heterogeneous multicore chips.

Despite this widespread availability of heterogeneous multicore processors and the eagerness to use them, their use in embedded real-time systems is non-trivial. One of the major challenges is that many embedded systems have real-time requirements and it must be proven before run-time that these requirements are satisfied at run-time. The way applications are scheduled significantly influences whether their timing requirements are satisfied.

The real-time community is starting to take some initial steps in developing scheduling algorithms and analysis techniques for heterogeneous multicores. This talk gives an overview of the on-going effort in the community in this direction. In particular, it will discuss a couple of solutions that have been recently proposed by researchers by highlighting the key techniques that were used in developing these solutions. It concludes by providing a glimpse of open problems.

Bio

Gurulingesh Raravi is currently a Research Associate at CISTER Research Centre in Porto. He received the Doctorate degree from University of Porto in 2014. He has worked in industry both prior to and after his PhD for about 5+ years in designing solutions for a variety of problems encompassing domains such as cyber-physical systems and services computing. His research interests include embedded real-time systems, resource allocation and sharing in distributed systems, algorithms, and optimisation.

11:15am — Coffee break

- 11:30 — “A Novel Architecture for Highly-Scalable, Secure, and Real-Time Systems-on-Chip.”, Soultana Ellinidiou, Xavier Poczekajlo, Gaurav Sharma, Georgios Bousdras, Jean-Michel Dricot, Joël Goossens, Olivier Markowitch, Dragomir Milojevic & François Quitin (ULB).

- 12:00pm - “FPGA as Image Signal pre-Processors for Smart Cameras based Applications”, Naim Hard & Carlos Valderrama (UMons).

- 12:30pm Lunch

- 1:15pm — “Hard real-time scheduler for sporadic task sets on heterogeneous platforms, and multimode systems”, Xavier Poczekajlo & Joël Goossens (ULB).

- 1:45pm - “Binding Design and Analysis by Viewpoints for Heterogenous Real-Time systems”, Anh-Toan Long, Yassine Ouhammou & Emmanuel Grolleau (ENSMA).

- 2:15pm - “Mapping avionics functions on a mixed NoC/AFDX architecture”, Laure Abdallah, Jérôme Ermont, Jean-Luc Scharbard & Christian Fraboul (IRIT)

- 2:45pm — Coffee break

- 3:15pm — “Can we get a predictable cache system for real-time computer systems?”, Yannick Allard, Dragomir Milojevic & Joël Goossens (ULB).

- 3:45pm — “Research and implementation challenges of RTOS support for heterogeneous computing platforms”, Martin Cornil, Antonio Paolillo, Joël Goossens & Ben Rodriguez (Hipperos/ULB).

- 4:15pm Closing remarks

- Joël Goossens (ULB, Brussels, Belgium)

- Pierre Manneback (UMons, Mons, Belgium)

- Dragomir Milojevic (ULB, Brussels, Belgium)

- 10am – Welcome & Coffee

10:30am – Keynote Talk

“Multi-Core Timing Verification via Interference Modelling — Predicting the unpredictable”

By Prof. Sebastian Altmeyer (University of Amsterdam, NL)

- 12:00am – Lunch

- 1:30pm — “Real-time systems’ stress testing detecting worst case latencies using statistical methods”, Luc Perneel and Martin Timmerman (VUB)

- 2:10pm - “Toward an Efficient Data Plane for Memory Systems Interference Regulation in COTS Multi-core Systems”, Cedric Courtaud, Julien Sopena, Gilles Muller and Daniel Gracia-Perez (Inria, Sorbonne, Thales)

- 2:50pm — Coffee Break

- 3:10pm — “Dynamic Arbitration of Memory Requests with TDM-like Guarantees”, Farouk Hebbache, Mathieu Jan Florian, Brandner and Laurent Pautet (CEA & ParisTech)

- 3:50pm — “Tightening contention delays while scheduling parallel applications on multi-core architectures”, Benjamin Rouxel (University of Rennes 1)

- 4:30pm — Conclusion

- Joël Goossens (ULB, Brussels, Belgium)

- Pierre Manneback (UMons, Mons, Belgium)

- Juan M. Rivas (ULB, Brussels, Belgium)

- 9:30am – Welcome & Coffee

10:00am – Keynote Talk

“Phylog project: an argumentation-based methodology for multi-core COTS”

- 11:00am Coffee

11:20am Junior Presentations

- Nathanaël Sensfelder, Julien Brunel, Claire Pagetti (ONERA, France): “On How to Identify Cache Coherence: Case of the NXP QorIQ T4240”

- Matheus Schuh (VERIMAG/Kalray): “Implementation of Real-Time Data-Flow Synchronous Programs on a Many-Core Architecture”

- Suhail Nogd, Geoffrey Nelissen, and Mitra Nasri (TUDelft and CISTER): “A Schedule Abstraction Graph Analysis Considering Shared Resource Accesses in Multicore Platforms”

- Joan Marcè i Igual, Geoffrey Nelissen, Mitra Nasri, and Paris Panagiotou (TUDelft and CISTER): “Scheduling and Analysis of Limited-Preemptive Moldable Gang Tasks”

- Eghonghon Eigbe, Suhail Nogd, and Mitra Nasri (TUDelft): “On the Partitioned and Semi-Partitioned Scheduling of Non-preemptive Periodic Tasks upon Multicore Platforms”

12:20am Lunch

- Invited Talks

- 1:20pm Benjamin Lesage, Iain Bate and Rob Davis (York University, UK): “Modelling task characteristics on multicore systems”

- 1:50pm Benjamin Rouxel (University of Amsterdam, NL): “RT-Engineering: the art of timing control”

- 2:20pm Jan Reineke (Saarland University, Germany): “Provably Timing-Predictable Microarchitectures”

- 2:50pm Coffee Break

- 3:10pm Mathieu Jan (CEA, France): “Tracking timing anomalies”

- 3:40pm Selma Saidi (TU Dortmund, Germany): “Formal Performance Analysis of High-Performance Heterogeneous MPSoCs”

- 4:10pm Panel Discussion

- Joël Goossens (ULB, Brussels, Belgium)

- Claire Maiza (Grenoble INP/Ensimag, Verimag, Grenoble, France)

Real-Time Networks Seminar (FNRS Contact Group)

by Luis Almeida

From Fri 27 May 2016 10:00 to Fri 27 May 2016 17:00

A one-day seminar will take place within the framework of the Belgian FNRS Contact Group “Embedded Real-Time Systems” and the GRASCOMP doctoral school (Belgium's French Community).

The workshop offers a round table for exchanging ideas and foster discussions around the theme of real-time network, including (but not limited to): real-time message scheduling, Ethernet, CAN, FlexRay, networked embedded systems and sensor networks, among others. The format of the seminar encourages interaction between participants and open discussions.

Free but mandatory registration (by May 19th)

Program

Venue

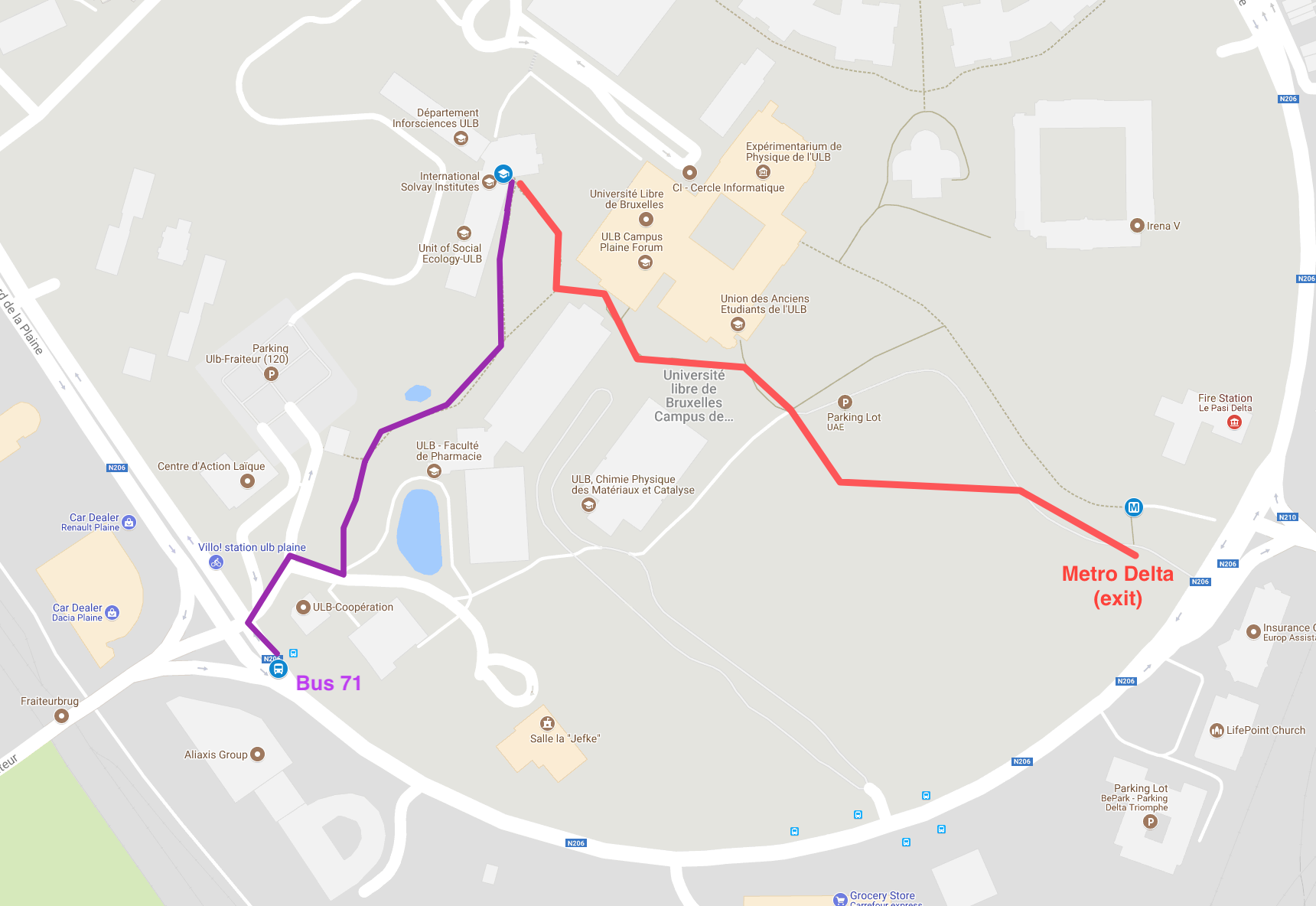

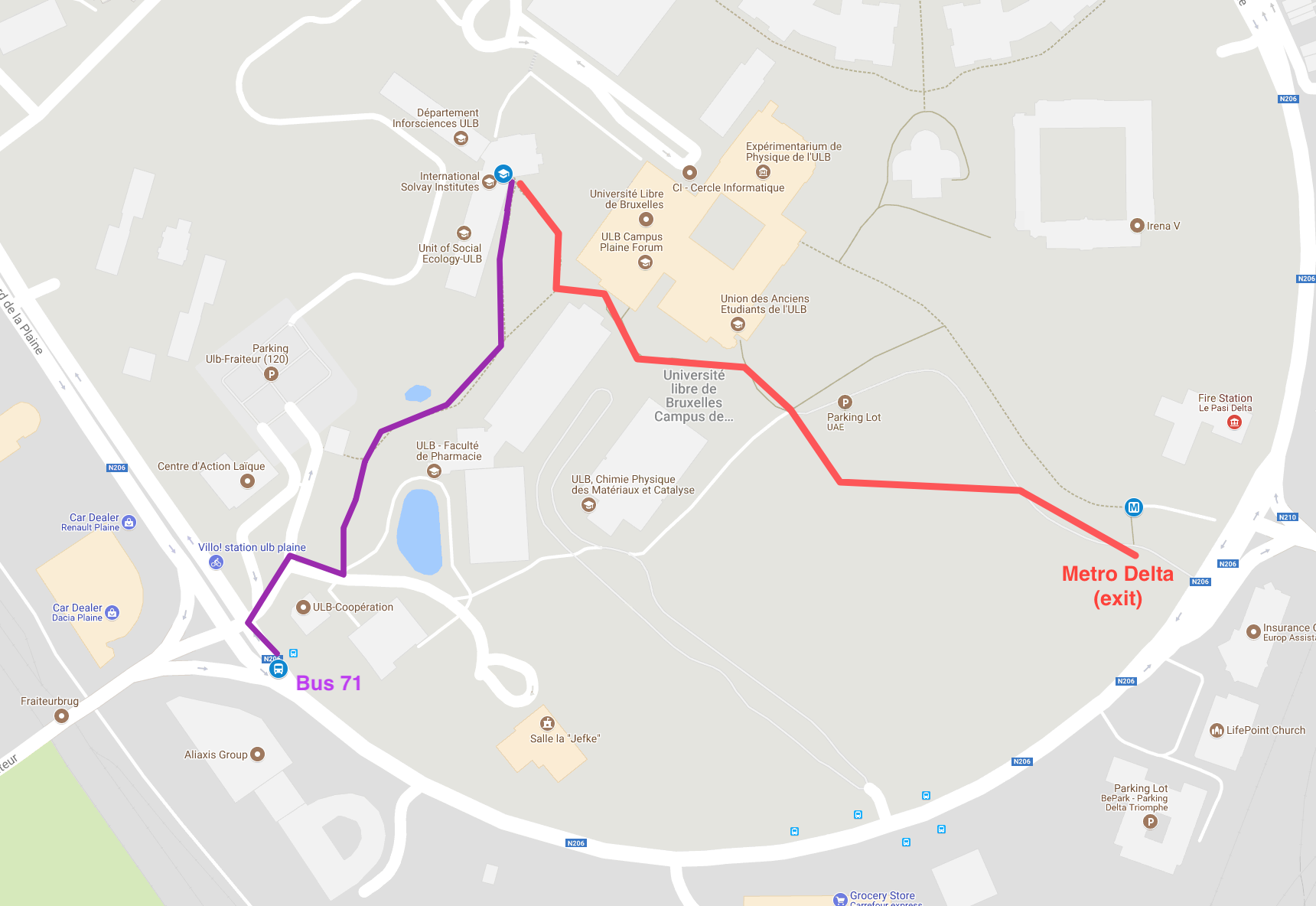

The seminar will be held NO building (5th floor, Solvay room), “campus de la Plaine” ULB, Brussels.

By subway: Line 5, “Hermann-Debroux” direction, stop “Delta”

By train: fast trains (Thalys, TGV, Eurostar, ...), stop Bruxelles-Midi train station. Then subway Line 2 or 6, “Elisabeth” direction, exit at “Arts-Loi”, then line 5, “Hermann-Debroux” direction, stop at “Delta”. (about 1/2 hour).

Hotels

Suggestions:

Committee

Further information

Friday May 27th 2016.

9:30am — 4:30pm

Solvay room, ULB, plaine campus, building NO, 5th floor

Contact the chair person joel.goossens@ulb.ac.be

Cycle de développement logiciel critique et temps réel : un exemple de mise en œuvre en avionique

by Emmanuel Grolleau

From Fri 3 Jun 2016 16:00 to Fri 3 Jun 2016 18:00

Salle de vidéoconférence, UB2.129, campus du solbosh, ULB

Professeur invité

Emmanuel Grolleau, ISAE-ENSMA (Institut Supérieur de l'Aéronautique et de l'Espace, École Nationale Supérieure de Mécanique et d'Aéronautique), LIAS (Laboratoire d'Informatique et d'Automatique pour les Systèmes)

Résumé de l'exposé

Le secteur aéronautique et aérospatial est très développé en France, ce pays a développé un savoir-faire avec l'apparition du Concorde et de la Caravelle, savoir-faire depuis remisé sur l'ensemble des aéronefs d'Airbus. La recherche fondamentale et industrielle est dès lors très importante aussi et couvre un très large spectre. Nous nous intéressons ici à l'informatique, aux logiciels embarqués qui doivent dans ce secteur être certifiables et respecter des contraintes temporelles fortes. Dans cette présentation, nous considérons du logiciel embarqué critique et temps réel.

Dans l'avionique, ainsi que dans de nombreux secteurs du logiciel embarqué critique, le cycle logiciel typique part d'exigences, puis exprime une décomposition fonctionnelle en utilisant une sémantique flots de données ou non, indépendamment du matériel sous-jacent. La conception du matériel/logiciel est la prochaine étape vers l'implémentation du système embarqué. Pour les systèmes critiques, typiquement en aéronautique, des langages de description d'architecture (ADL) sont utilisés pour décrire les interactions entre les différents artefacts logiciels et comment le logiciel est déployé sur le matériel. Une important étape de la conception est donc d'allouer les fonctions aux tâches, les tâches aux calculateurs(éventuellement aux partitions de calculateur pour ARINC 653), et les messages aux réseaux.Les ADL proposent des concepts qui sont proposés par la plupart des noyaux temps réels (RTOS). Lorsque les choix de conception sont effectués, il existe de plus en plus d'outils technologiques permettant de faciliter la génération automatique ou semi-automatique de code(model to text). Cette présentation se conclura par les différentes modélisations temporelleseffectuées à partir de la conception d'un système exprimé dans un ADL.

Public visé

L'exposé vise un large public avec des bases en sciences informatiques, cela comprend les étudiants de la Faculté des Sciences en informatique à partir du BA2, les étudiants de l'École polytechnique à partir du BA3 et les chercheurs en sciences informatiques.

Informations pratiques

le 3 juin 2016.

de 16h à 18h.

Call for Participation: Heterogeneous Architectures and Real-Time Systems Seminar (FNRS Contact Group)

From Fri 5 May 2017 10:00 to Thu 5 May 2016 17:00

A one-day seminar will take place within the framework of the Belgian FNRS Contact Group “Embedded Real-Time Systems” and the GRASCOMP doctoral school (Belgium's French Community).

The workshop offers a round table for exchanging ideas and foster discussions around the theme of heterogeneous architectures and real-time systems, including (but not limited to): real-time scheduling, NoC, and embedded real-time electronics, among others.

Free but mandatory registration (by May 1st 2017)

Program

Committee

Venue

The seminar will be held NO building (5th floor, Solvay room), “campus de la Plaine” ULB, Brussels.

By subway: Line 5, stop “Delta”.

By train: fast trains (Thalys, TGV, Eurostar, ...), stop Bruxelles-Midi train station. Then subway Line 2 or 6, “Elisabeth” direction, exit at “Arts-Loi”, then line 5, “Hermann-Debroux” direction, stop at “Delta”. (about 1/2 hour).

Hotel Suggestions:

Important information

Friday May 5th 2017.

9:30am — 4:30pm

Solvay room, ULB, plaine campus, building NO, 5th floor

Follow this page parts.ulb.ac.be/pages/events.html#HARTS-ULB-2017 or contact the chair person (E-mail: joel.goossens@ulb.ac.be)

Call for Participation (FNRS Contact Group): The NExt Step TOwards multi-core Real-time systems (NESTOR)

From Fri 18 May 2018 10:00 to Wed 18 May 2016 17:00

Friday May 18th, 2018. A one-day seminar will take place within the framework of the Belgian FNRS Contact Group “Embedded Real-Time Systems” and the GRASCOMP doctoral school (Belgium's French Community).

The workshop offers a round table for exchanging ideas and foster discussions around the theme of predictable solutions for Multi-core processors.

Free but mandatory registration (by May 9th 2018)

Programme

Keynote's Abstract

Multicore architectures are considered the future in the embedded real-time domain. Yet, the need for timing verification hampers their adoption: Multicores are considered inherently unpredictable, whereas predictability is often considered a prerequisite for real-time systems. We will therefore have to find fundamentally new techniques to verify the timing correctness of multicore systems.

In this presentation, we will first go one step back and (i) revisit the motivation behind using multicore systems in the embedded real-time domain and (ii) the approach to timing verification for single-core systems. Then, we will discuss the implications of this motivation, and potential trade-offs between analysis time and precision. Finally, we will present a multicore timing verification framework based on interference modelling. The framework first (conceptually) decomposes the multicore processor into its timing-relevant components, analyses the components' impact on a program's timing behaviour, and then constructs the overall timing behaviour of a multicore architecture based on the timing behaviour of its components.

Sebastian Altmeyer's Bio

Sebastian Altmeyer is Assistant Professor (Universitair Docent) at the University of Amsterdam. He has received his PhD in Computer Science in 2012 from Saarland University, Germany with a thesis on the analysis of preemptively scheduled hard real-time systems. From 2013 to 2015 he has been a postdoctoral researcher at the University of Amsterdam, and from 2015 to 2016 at the University of Luxembourg. In 2015, he has received an NWO Veni grant on the timing verification of real-time multicore systems, and he is program chair of the Euromicro Conference on Real-Time Systems (ECRTS) 2018. His research targets various aspects of the design, analysis and verification of hard real-time systems, with a particular interest in timing verification and multicore architectures.

Committee

Venue

The seminar will be held NO building (9th floor, Salle des professeurs), “campus de la Plaine” ULB, Brussels.

By subway: Line 5, stop “Delta”, exit 2.

By train: fast trains (Thalys, TGV, Eurostar, ...), stop Bruxelles-Midi train station. Then subway Line 2 or 6, “Elisabeth” direction, exit at “Arts-Loi”, then line 5, “Hermann-Debroux” direction, stop at “Delta”. (about 1/2 hour).

Hotel Suggestions:

Important information

Friday May 18th 2018.

10am — 4:30pm

Salle des professeurs, ULB, plaine campus, building NO, 9th floor

Follow this page parts.ulb.ac.be/pages/events.html#NESTOR-ULB-2018 or contact the chair person (E-mail: joel.goossens@ulb.ac.be)

FNRS Contact Group: sCalable And PrecIse Timing AnaLysis for multicore platforms (CAPITAL)

From Mon 24 Feb 2020 09:30 to Mon 24 Feb 2020 17:00

Monday February 24th, 2020. A one-day seminar will take place within the framework of the Belgian FNRS Contact Group “Embedded Real-Time Systems”, the GRASCOMP doctoral school (Belgium's French Community), and Verimag Lab (Grenoble, France).

The workshop offers a round table for exchanging ideas and foster discussions around the theme of sCalable And PrecIse Timing AnaLysis for multicore platforms.

Abstract

The design and the implementation of time-critical applications upon multi-core processors are considered. Multi-core processors have the potential to offer high computing power. Unfortunately, their extensive use of shared resources (e.g., caches, DRAM, buses, etc.) makes the design and the implementation difficult to predict — especially in situations where hard real-time constraints must be satisfied. Recent works show that an important challenge is to design a precise and scalable timing analysis. To address this challenge the research community consider closely both sides of the system: software and hardware. The aim of this co-design approach is therefore to guarantee scalability, precision and low complexity of the solution without compromising flexible efficient use of resources. The solution must be tailored for the target application and platform. In particular by identifying the shared resources (memory, bus, cache) and by reducing the complexity based on interference delay using, for instance, a tailored mapping/scheduling, bandwidth regulator. The solution must be also based on a good use of the hardware architecture (memory banks, cache, communication media) with techniques like physical/temporal partitioning to obtain a precise solution.

Free but mandatory registration by Monday February 17th, 2020

Register here

Programme

Abstracts

Phylog project: an argumentation-based methodology for multi-core COTS (Claire Pagetti)

The PHYLOG project aims at offering a model-based software-aided certification framework for aeronautical systems based on multi/many-core architectures. Certifying such platforms will entail fulfilling the high level objectives of the MCP CRI/CAST 32A position paper. To reach this general objective, we have defined a certification framework based on patterns to express any argumentation; as well as formal and automatic analyses to support the proof of the argumentation. In this presentation, we will introduce the certification methodology and look at two types of analysis required by the MCP CRI: interference and safety analyses.

Tracking timing anomalies (Mathieu Jan)

Computer architectures used in safety-critical domains are subjected to worst-case execution time analysis. The presence of performance-driven microarchitectures may trigger undesired timing phenomena, called timing anomalies, and complicate the timing analysis. In this talk, we introduce two types of such undesired timing phenomena, called counter-intuitive and amplifications timing anomalies at the pipeline level. We then present our approach to detect these differents types of timing anomalies within programs running over various pipelines, in particular the designed abstract formal hardware models as well as the verification strategy based on model-checking.

RT-Engineering: the art of timing control (Benjamin Rouxel)

Guaranteeing timing properties for embedded real-time systems is a real challenge. It involves many information from the software, hardware and execution environment such as the Operating System (OS). People from the real-time community built a huge amount of nice analyses including, among others, Worst-Case Execution Time (WCET) analyses accounting for each individual part of specific hardware, schedulability analyses for a variety of off-line and on-line schedulers. But when it goes to actually using these analyses on a real industrial use-case, what is left of them? Many of industrial use-cases do not fully match these nice analyses or task models for many reasons, including exotic hardware, software libraries targeting general purpose computing, or OS with timing hazards. I will derive on a real use-case, given by one of the many partners from the H2020 TeamPlay projects, all the tweaks that we needed to perform at every level in order to reach some form of timing guarantees.

Provably Timing-Predictable Microarchitectures (Jan Reineke)

Microarchitectures are commonly not designed with timing predictability in mind. As a consequence, performance-enhancing microarchitectural features in modern processors such as caches and pipelining often result in unpredictability.

In this talk, I will discuss design principles that enable timing predictability and how to automate timing-predictability proofs using SMT solvers.

Modelling task characteristics on multicore systems (Benjamin Lesage)

Understanding how tasks sharing processing resources interact with each other is a key challenge in the context of multi-core processors as interferences between cores can lead to large variations in execution times. For the certification of safety-critical systems, it is key to understand the interference channels on a platform, and to assess how they might affect a specific task. The Forecast-Based Interference analysis framework defines a process for the characterisation of such a platform, feeding into the model of a task's behaviour in presence of interferences. The approach relies on measurement-based techniques to alleviate the limited information that may be available on the platform.

Formal Performance Analysis of High-Performance Heterogeneous MPSoCs (Selma Saidi)

Timing analysis approaches are commonly used to bound the timing behavior of safety-critical systems in the worst-case considering a model of the hardware platform and worst-case interference scenarios of tasks sharing resources in the system. As the complexity of the used hardware platform increases, the gap between existing timing analysis methods and the numerous architectural hardware details influencing the timing behavior of the system is also increasing. Many existing approaches in embedded systems design have previously rely on the worst-case execution time (WCET) abstraction as an interface between the software and hardware where the timing effect of shared hardware components is captured during code-level analysis and concealed in the WCET of a task. This abstraction was valid for many years where micro-controllers platforms were predominant. However, with the advent of complex heterogeneous MPSoCs architectures, the performance effects due to micro-architecture choices, shared resources, interconnects, and memory hierarchy are becoming a dominant factor. Therefore, one major challenge for existing modeling and analysis frameworks is to capture the appropriate hardware parameters that influence performance and be able to model and analyze hardware components. In this talk, we discuss the current practices in timing analysis of shared hardware resources and show the limitations of these techniques that only consider abstract notions of tasks, resources and tasks activation, compliant with the classical formulation of the single processor multi-task scheduling problem. We show then how standard system-level performance analysis techniques can be extended to consider hardware features and analyze networks-on-chips as well as shared memory systems in MPCoCs.

Organisers

Venue

The seminar will be held NO building (5th floor, Salle Solvay), “campus de la Plaine” ULB, Brussels.

By subway: Line 5, stop “Delta”, exit 2.

By train: fast trains (Thalys, TGV, Eurostar, ...), stop Bruxelles-Midi train station. Then subway Line 2 or 6, “Elisabeth” direction, exit at “Arts-Loi”, then line 5, “Hermann-Debroux” direction, stop at “Delta”. (about 1/2 hour).

Hotel Suggestions:

Important information

Monday February 24th 2020.

9:30am — 5:00pm

Salle Solvay, ULB, plaine campus, building NO, 5th floor

Follow this page parts.ulb.ac.be/pages/events.html#CAPITAL-ULB-2020 or contact the chair person (E-mail: joel.goossens@ulb.ac.be)